# **特集** 広帯域移動アクセスシステム( CSMA )における符号器の 開発\*

Development of Coders/Decoders on the Broad Band Mobile Access Communication System (CSMA) Standard

河合茂樹 澤田 学 佐々木邦彦

higeki KAWAI Manabu SAWADA Kunihiko SASAKI

A broad band mobile access communication system with a maximum speed of 36Mbit/s is expected to apply to a large number of broad band appliances. The decoding methods of this system are so complex that they overgrow the latency. Generally the latency results in deterioration of the system performance. We have contrived the predicating decoding algorithm which improves the transmission performance.

Key words: Low latency decoder, Viterbi decoder, IEEE802.11a, ARIB STD-T71

## 1.まえがき

NTT ドコモの次世代携帯 (FOMA)の本格運用が始まるなどディジタル携帯電話の爆発的な普及に加え,ADSLなどのブロードバンドサービスの急速な普及で,超高速モバイルインターネットサービスへの要求が高まっている.

このような背景で,最大伝送速度11 Mbit/sの無線 LAN(IEEE802.11b)による公衆・自営スポットサー ピスが全国的に展開し始め,一方,自動車通信分野に おいても,高速道路の自動料金収受(ETC)やそれを 拡張したDSRCが開発され実用化されている.

筆者らは,このような社会の要求に対応するため, さらに超高速な無線インターネットの研究を1998年より取り組んできた.OFDM(Orthogonal Frequency Division Multiplexing)方式という新しい通信方式と 5 GHz帯無線を用いることで,ハイビジョンテレビ品 質の映像をリアルタイム伝送することも可能になり, モバイル・ショッピングだけでなく,交差点渋滞映像 の参照や家のパソコンから車に自作のドライブプラン を送る新しいカーナビへの応用提案などを行っている.

さらに,1999年10月に5GHz帯高速無線LAN標準規格であるIEEE802.11aおよび同国内標準規格ARIB STD-T71に準拠した無線実験装置を試作し,技術基準適合証明を取得した.

本論文では,同実験装置の主要コンポーネントであるディジタル符号処理のハードウェア化にかかわる課題について解説する.

ディジタル符号化とは,不安定な無線通信路上で生じる誤りを数値演算によって訂正し,正しい情報を再

生する処理をいう.信頼性の高い通信を行うために重要な処理であり,システム全体のパフォーマンスに大きく関与する.

今回,分岐枝の並列実行を行う復号アルゴリズムにより,従来に比べて大きくレイテンシを軽減したので, そのハードウェア構成を中心に述べる.

## 2.無線通信システムと誤り訂正符号

#### 2.1 誤り訂正符号とは

ディジタル2値情報を1ビットの誤りもなく確実に 伝送するシステムでは、外部からもたらされるさまざ まな擾乱によって引き起こされる伝送誤りの検出、あ るいは誤りの発生した情報を本来の情報に回復するた めの訂正は重要な問題である.

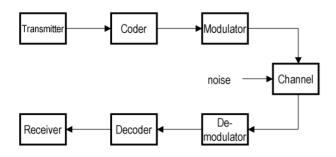

一般に、誤り通信路を含む通信システムのモデルは Fig. 1のようにして表される・ディジタル無線通信システムにおける通信路(channel)は、極めて外乱の 大きなアナログ通信路である・ディジタル情報は通信 路で伝送しうるアナログ波形に変換する・この過程を 変調(modulation)と呼び、受信側で変調された波形 を元の形に復元することを復調(demodulation)と呼ぶ・

復調では通信路の外乱によって誤りが生じることがあり、この誤りを検出および訂正するためにディジタル情報に何らかの変換を行うことを符号化(coding /encoding),通信路から出力された符号化情報を再生することを復号(decoding)と呼ぶ、符号化には、情報を第3者から秘匿するための暗号化を含むこともある、以後、符号化・復号を行う機能プロックをそれぞれ符号器(coder/encoder)・復号器(decoder)と呼ぶ、

<sup>\* 2003</sup>年3月10日 原稿受理

Fig. 1 System model of communication system

# 2.2 符号器・復号器への要求条件 通信システム内における符号化に対する要求は,

(1)信頼性の向上

#### (2)効率の向上

を達成するための変換方法を選択・実装することにある.ディジタル無線通信システムにおいて,信頼性とはすなわち低い誤り率を,効率とは変換効率(少ない冗長度と処理時間)を意味する.

しかし,この二つは本来背反する要求であり,両方を同時に達成することは非常に難しい.通信システム全体に求められる要求とハードウェア・ソフトウェアの規模や負荷を考慮した上で,最適な符号化方式や実装方法を探らなければならない.

## 2.3 高速無線LAN実験機概要と構成

IEEE802.11aおよびARIB STD-T71 [小電力データ通信システム/広帯域移動アクセスシステム(CSMA)]は,1999~2000年に標準規格化された無線通信システムである.5 GHz帯を利用し,変復調方式にOFDMを採用して無線の対マルチパス特性を向上した高速無線LANとして今後の機器普及が見込まれており,我々はこの規格をベースに広帯域移動アクセスシステム実験機の開発を行うこととした.

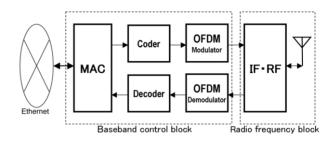

実験機の構成と基本仕様をFig. 2, Table 1に示す. 伝送方式は5.2GHz帯を用いたOFDMであり,マルチパスに強く大容量移動体通信を実現するのに適していると考えられる.

伝送データレートは最大36Mbit/s,符号化は畳込み符号 (convolutional code) によって行い,アクセス方式としてCSMA/CA (Carrier Sense Multiple Access with Collision Avoidance) を採用している.これら基本仕様はARIB STD-T71に準拠している.

MAC (Medium Access Control)を通じて入力された情報は符号器・OFDM変調器・高周波回路 (RF・IF)を通じて送信を行い、受信側ではRF・IFから

OFDM復調器,復号器によって元の情報を再生して MACから再びネットワークに伝える.超高速伝送の ほか,通信路状態に合わせて適応的にデータレートを 変化させるマルチデータレート扱えることが特徴として挙げられる.

Fig. 2 System configuration of demonstrator

Table 1 Specification of demonstrator

| Radio frequency     | 5.15-5.25GHz(4ch)                  |

|---------------------|------------------------------------|

| Band width          | 16.5MHz                            |

| Output power        | 15mW                               |

| Antenna             | omni                               |

| Modulation scheme   | OFDM(BPSK, QPSK, 16QAM)            |

| Subcarriers         | 52 (within 4 pilot carriers)       |

| Demodulation scheme | synchronous detection              |

| Coding scheme       | convolutional code(R=1/2,3/4, K=7) |

| Data rates          | 6Mbit/s(BPSK,R=1/2)                |

|                     | 9Mbit/s(BPSK,R=3/4)                |

|                     | 12Mbit/s(QPSK,R=1/2)               |

|                     | 18Mbit/s(QPSK,R=3/4)               |

|                     | 24Mbit/s(16QAM,R=1/2)              |

|                     | 36Mbit/s(16QAM,R=3/4)              |

| MAC protocol        | CSMA/CA                            |

| NW interface        | ethernet(100Base-TX)               |

## 2.4 符号器・復号器の構成

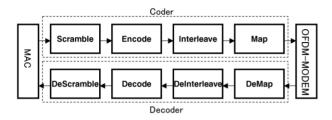

実験機の符号器・復号器は、Fig. 3の構成によって 実現する。符号器に入力されたディジタル2値情報は、 Encodeによって冗長情報を付加したディジタル情報 に変換する。パースト誤り時の訂正効果を高めるため、 Interleaveによって情報ビットの並び順を交換する。 Mapによってディジタルビット列情報はアナログ波形 の振幅と位相に対応するように割り当て、OFDM変調 部へと出力される。受信側の復号器では、送信側とまったく逆の手順(DeMap、DeInterleave、Decode) によって元の情報を再生するが、この際のDecode処 理によって通信路上で混入した誤りが訂正される。

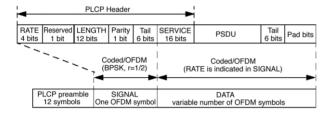

また、マルチレート対応のためにパケットフォーマットはFig. 4のようになっている。固定レート SIGNAL部に記述されたRATE情報によって可変レートDATA部のデータレートを示す仕組みになってい る.データレートは, Mapでのアナログ波の振幅・位相へのディジタルビット列の割当方法(変調方式)と, Encodeで符号化する際の冗長情報付加率(符号化レート)を選ぶことで変えることができる.

Fig. 3 System configuration of coder and decoder

Fig. 4 Frame format of communication packet

## 2.5 畳込み符号とビタビ復号

実験機では、符号化方式として畳込み符号を用いる. 有限オートマトン内部状態と過去の入力情報系列に依存した符号化を行うことで、出力系列はトレリス線図と呼ばれる木構造にマッピングされる.トレリス線図上の情報系列は、ビタビ(Viterbi)アルゴリズムとして知られる最尤復号法を用いることで元の情報系列を再生できる.畳込み符号化およびビタビ復号は非常に誤り訂正能力が高い符号化方式として、誤りの多い通信路を持つシステムに採用されることが多い.

## 3. 符号器・復号器ハードウェアへの要求条件

実験機ハードウェアに実装する上での通信路符号化 に対する要求条件を適用した場合についての課題は次 のようになる.

#### 3.1 信頼性要求

通信誤り率特性の理論値は、規格仕様によって決定される。実際のハードウェアでは有限長のビット長しか扱えないことから、Demap時の判定ビット精度とハードウェア量のトレードオフが発生する。実験機においては、このビット精度は理想値である無限値に比べて符号化利得が0.2dB劣るだけの8値を用いている。

$1.0 \times 10^{\circ}$ の誤り率における伝送速度36Mbit/s (符号化レートR=3/4)時の符号化利得は約4.6dBとなり,無線設計上のマージンをその分大きく確保することができる.

#### 3.2 効率要求

符号化によって付加される冗長情報は伝送レートごとに割合が決まり,符号化レートR=1/2および3/4の2種が定義されている.R=1/2に比べてR=3/4の方が冗長度が低く情報伝送効率は高いが,誤り訂正能力は低い.これらは伝送路状態と送信情報の性質によって適応的に選択する.

しかし,ハードウェア化にあっては,符号器・復号器の実行にかかる実時間が全体の効率に与える影響が無視できず,慎重に検討しなければならない.

連続処理系システムにおけるレイテンシ(処理遅延時間)を、データ入力を行ってからそれに対応する出力が出るまでの時間と定義する.一般に連続同期処理系ハードウェアは内部がパイプライン化されており、レイテンシは少なくとも1(クロック時間)以上である.そして復号器、特にDeInterleaveとDecodeにかかるレイテンシがシステム全体の中でも非常に大きな割合を占めている.

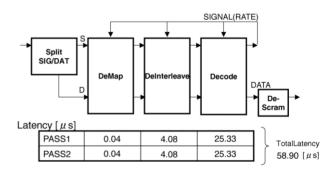

Decodeクロックをデータレート同期,ビタビアル ゴリズムのトレースバック長を48に設定した場合の構 成とレイテンシの見積はFig. 5である.

Fig. 5 System configuration and latency time of conventional decoder

## 3.3 レイテンシと全体の効率への影響

今回の実験機のシステム設計において,復号器に与 えるレイテンシマージンは16μs以下としている.

これは,実験機が採用するアクセス方式CSMA/CAのプロトコルに起因し,送受信機レイテンシが通信全体へ与える効率影響が大きいため,かなり小さい(厳

## しい)値に設定している.

CSMA/CAでは,伝送路を監視して空いているとき にだけ送信する物理キャリアセンス (Physical Carrier Sense ) 制御によるデータ送信およびACK (ACKnowledge) 受信の手順に先立ち,隠れ端末問題 回避のためにRTS (Request To Send)送信とCTS (Clear To Send) 受信によるヴァーチャルキャリアセ ンス (Virtual Carrier Sense) によるアクセス制御を行 う.一つの情報パケットに際して最低4回の無線パケ ットが交換される.このとき,それぞれの無線パケッ トの間隔をSIFS (Shorets Inter Frame Sequence)時 間と呼び、この時間が長ければ長いほど伝送路のスル ープット(伝送路ビットレートに対する実効ビットレ ートの比)が悪化してしまう.送受信機レイテンシの 短縮はそのまま無線機の実効効率の向上につながるた め、送受信機の構成部分毎にレイテンシマージンを設 定し,無線機全体でSIFS時間内に完了するようにハー ドウェアを設計しなければならない.

#### 3.4 低レイテンシ復号の必要性

今回採用した復号器プロックの構成によるレイテンシ見積 (Fig. 5) によれば,マージンを大きく超えた値になっている.この復号器を用いる限り,伝送を大きく落とす要因となる.

以上のことから,復号レイテンシを設計規定値(16  $\mu$ s)未満に低減するためのアルゴリズムの開発が必要である.

## 4. 低レイテンシ復号器

### 4.1 PredicativeDecoding手法の提案

復号レイテンシの短縮のためにさまざまな手法が提案されているが、いずれもシングルレート受信機に最適化して見かけ上のレイテンシを隠蔽することが目的となっており、実験機にはそのまま適用することができない.

また,不定期に到来するデータパケットを高速に連続的に処理する必要があるため,CPUを用いたハードウェア構成もとりにくい.

ビタビデコーダ自身の実装アルゴリズムを変更して レイテンシを短縮するのは有効であるが,信頼性の確 保の点から今回の検討対象外とした.

そこで,復調レートと符号化レートの選択が有限であることに着目し,必要な分岐先処理を並列実行によって先に求め,条件が確定してから選択するPredicative Decodingを用いて全体のレイテンシおよびスループットを向上する方法を提案する.

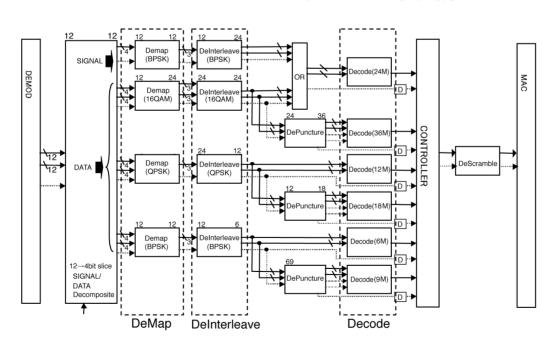

#### 4.2 Predicative Decoderの構成

Predicative Decodingをハードウェアにするためのブロック図をFig. 6に示す.変調方式・符号化レート別に複数のDeMap・DeInterleave・Decodeを動作させ,SIGNALとDATAの復号処理を同時に行う.こうすることで,従来SIGNAL復号を行ってデータレートを求めてからDATA復号を行う2PASSだったパケット

Fig. 6 Block diagram of Predicative Decoder

復号処理を,1PASSで行うことができる.

共通の処理を行うブロック,あるいは時分割で利用できるブロックはできる限り共有し,ハードウェアが 簡潔になるようにした.

## 4.3 PredicativeDecodingの効果

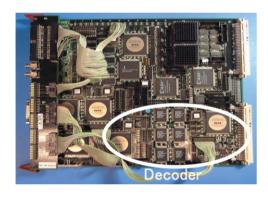

実際にPredicative Decoderをハードウェアとして試作した. Fig. 7は実験機に搭載した受信モジュールである. 10万ゲート相当のFPGAを2個,専用LSIを6個用いて実現している. 同様にして送信モジュールに搭載した符号器と組み合わせることにより, ARIB STD-T71準拠の情報伝送速度不定で任意のタイミングで到来するパケットを,遅滞なく逐次処理を行う仕組みを備えること特徴とする.

送信側で回線状態を監視して伝送品質悪化時に情報 伝送速度をフォールダウンする機能に対応するが,そ れをあらかじめ受信側に通知する必要がなく,オーパ ヘッドも少ない.

Fig. 7 Photograph of demodulation hardware with Predicative Decoder

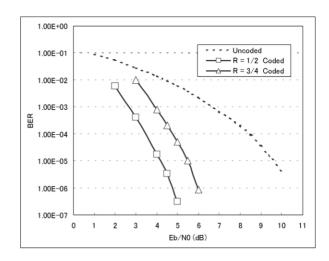

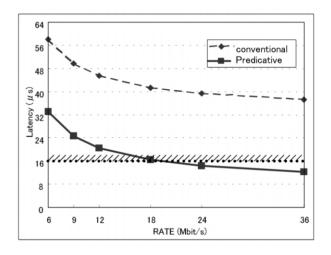

**この受信モジュールに搭載した復号器の性能を**Fig. 8 , Fig. 9 に示す .

Fig. 8 Coding gain of Predicative Decoder with reference to an uncoded BPSK

Fig. 9 Latency of Predicative Decoder with reference to a conventional decoder

信頼性においては、すべての誤り率において理論値に近い符号化利得(観測値/理論値<-0.2dB)を示しており、期待する性能を発揮している、効率においては、18Mbit/s以上のデータレートのときにレイテンシ目標値を満たしているが、12Mbit/s以下時に超えている、これは、Decodeがデータレート同期動作のため、低データレート時の動作速度が不足しているためである。しかし、Predicative Decodingを用いない復号器に比べてレイテンシは減少しており、効果を実証することはできている。

## 5.むすび

ARIB STD-T71準拠の5GHz帯高速無線アクセスシステムのベースパンド処理部における,符号器・復号

器の機能構成と装置構成を示した.この符号器・復号器は,不定期送出・到来パケットを最大36Mbit/sの速度で処理することができる.また,受信側においては復号器にPredicative Decodingを提案し,レイテンシ低減を図っている.この手法を用いた低減効果を実証し,信頼性(ビット誤り率)と,高データレート時に所望の効率(処理レイテンシ)を満たしていることを確認した.

今後の課題として,低データレート時のレイテンシ軽減,ハードウェア量の削減と消費電力の低減が挙げられる.低データレート時には,Decodeがデータレートと同期動作をしていることが原因となっているので,解決にはDecode動作クロックを上位のデータレートもしくはそれ以上に引き上げて非同期動作させるのが有効である.基板上の速度不整合は,デュアルクロックバッファとタイミング制御回路の追加によって対応できる.

ハードウェア量削減に関しては、分岐先処理 (Decode)に共通処理部分が多いことを利用したさら なる回路共有化をする余地があり、条件確定タイミン グで選択されない処理枝を中断することで消費電力を 低減することも考えられる。

今後は今回開発した符号器・復号器ハードウェアを 含む実験機の性能向上・小型化とチップ化を進めてい く.

## <参考文献>

- 1) IEEE Standard 802.11 Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) specifications, IEEE (1997)

- 2) IEEE Standard 802.11a High Speed Physical Layer(PHY) in the 5 GHz Band, IEEE (1999)

- 3) ARIB STD-T71 小電力データ通信システム / 広帯域 移動アクセスシステム (CSMA),電波産業会 (2000)

- 4) John G. Proakis, 坂庭好一他:ディジタルコミュニケーション,科学技術出版 (1999)

- 5) 井上徹他: 実戦 誤り訂正技術, トリケップス (1996)

- 6) 今井秀樹:情報理論,昭晃堂(1981)

- 7) 澤田学,桑原雅宏,松ヶ谷和沖,佐々木邦彦: "広帯域移動アクセスシステム (CSMA) 準拠実験 装置の試作",2001年電子情報通信学会 総合大会講 演論文集(2001),p.639.

## <著 者>

河合 茂樹 (かわい しげき)

基礎研究所 YRP情報通信研究室 無線通信システムにおける情報処理 アルゴリズム研究開発に従事

佐々木 邦彦 (ささき くにひこ)

基礎研究所 YRP情報通信研究室 ミリ波レーダ・無線通信システムな どの研究開発に従事

澤田 学 (さわだ まなぶ)

基礎研究所 YRP情報通信研究室 無線通信システムの研究開発に従事